Understanding Finite State Machines (FSMs): Types, Code & FAQs for Beginners

Description

Learn what Finite State Machines are, explore their types like Moore and Mealy machines, view example Verilog code, and get answers to common FSM questions.

Introduction

Finite State Machines (FSMs) are a fundamental concept in digital design, forming the backbone of many real-time systems like vending machines, traffic controllers, and communication protocols. For engineering students and aspiring VLSI designers, mastering FSMs is essential for understanding sequential logic and hardware behaviour. This blog covers the core concepts of FSMs, their types, a sample Mealy machine code, and frequently asked questions.

Core Sections

What is a Finite State Machine (FSM)?

A Finite State Machine is a sequential logic circuit that transitions between defined states based on input and clock signals. It has:

- Finite set of states

- Inputs and outputs

- State transition logic

- Clock and optional reset logic

FSMs are widely used in digital design, embedded systems, and VLSI due to their predictability and structured behavior.

Types of FSMs

- Moore Machine

- Output depends only on current state

- Simpler timing

- Outputs update after clock edge

- Example: Traffic light controller

- Mealy Machine

- Output depends on current state and input

- Faster output response

- Requires fewer states

- Example: Sequence detector

Note: Hybrid FSMs combine both Moore and Mealy logic for optimized designs.

Table differentiating types of FSM

Type | Output depends on | Typical use‑cases | Key point |

Moore machine | Current state only | Control units, pattern generators | Simpler timing; outputs change after the clock edge. |

Mealy machine | Current state and present input | Sequence detectors, hand‑shaking circuits | Fewer states; outputs may change inside the clock cycle. |

FSM Code Example

Mealy Machine – Overlapping Sequence Detector

Input

Design

//Pantech e-learning

//Mealy with overlapping code for the sequence 1101

module mealy(

input clk,rst,din,

output reg dout);

typedef enum logic [1:0] {s0,s1,s2,s3}state_;

state_ state,next;

always @(*) begin

next <= state;

dout <= 0;

case(state)

s0: begin

next <= (din)? s1:s0;

end

s1: begin

next <= (din)? s2:s0;

end

s2: begin

next <= (din)? s2:s3;

end

s3: begin

next <= (din)? s1:s0;

dout <=(din)? 1:0;

end

endcase

end

always @(posedge clk) begin

if(rst) begin

state <= s0;

end

else begin

state <= next;

end

end

endmodule

Testbench

//Pantech e-learning

module tb;

reg clk,rst,din;

wire dout;

mealy uut(.*);

initial begin

rst = 1;clk = 0;

#10 rst = 0;

end

initial begin

forever #5 clk = ~clk;

end

initial begin

din = 0;

#20;

din = 1; #10;

din = 1; #10;

din = 0; #10;

din = 1; #10;

din = 1; #10;

din = 0; #10;

din = 1; #10;

din = 0; #10;

din = 1; #10;

#10 $finish;

end

always @(posedge clk) begin

$display(“time = %t din = %b dout = %b”, $time,din,dout);

end

endmodule

Output

This FSM detects a sequence 1101 using an overlapping Mealy machine. Code includes state encoding, transition logic, and output generation in System verilog.

Applications of FSMs

- Digital circuit controllers

- Protocol encoders/decoders

- Elevator or traffic light logic

- Sequence detectors in communication systems

- Embedded system state control

Frequently Asked Questions(FAQs)

- What is the main difference between Moore and Mealy FSMs?

Moore’s output depends only on state, Mealy’s depends on state + input. - Why is Mealy preferred for sequence detection?

Because Mealy FSMs give faster response and require fewer states. - How can I avoid common FSM coding errors in Verilog?

Use non-blocking assignments (<=), reset all states, and provide default values in combinational blocks. - What are common uses of FSMs in VLSI design?

Control logic, data path steering, communication protocols, and error handling systems. - How many states should I use in an FSM?

Only as many as necessary to uniquely identify input history or system modes. State minimization helps reduce logic.

Conclusion

Finite State Machines are essential tools for digital logic designers. Understanding their types and structure helps you implement smarter hardware logic. Whether you’re building a vending machine controller or designing a VLSI testbench, FSMs are the go-to method for modelling sequential behavior.

Call to Action:

The Mealy FSM code (overlapping sequence detector) is available at this link. Simulate it yourself on EDA Playground and explore how the states and outputs behave in real time!

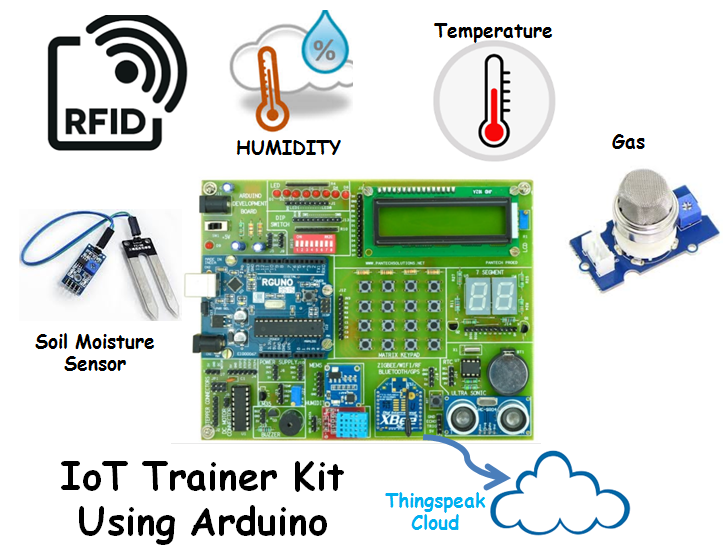

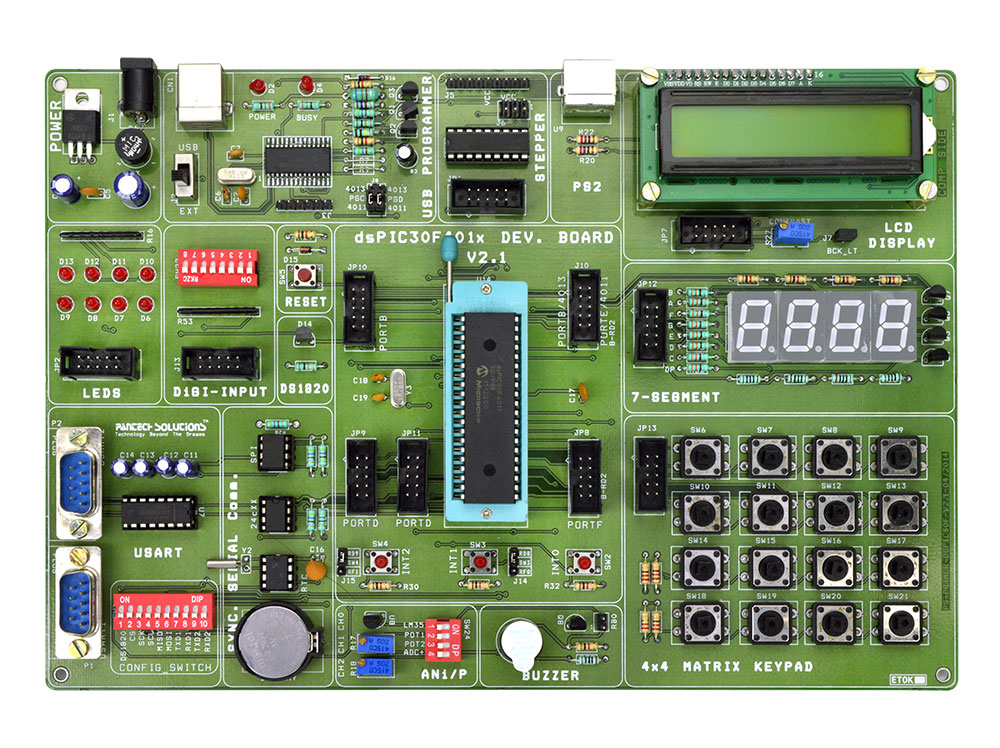

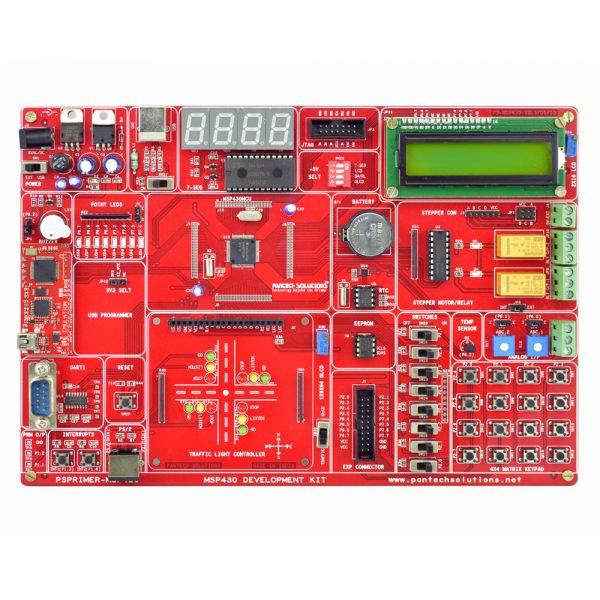

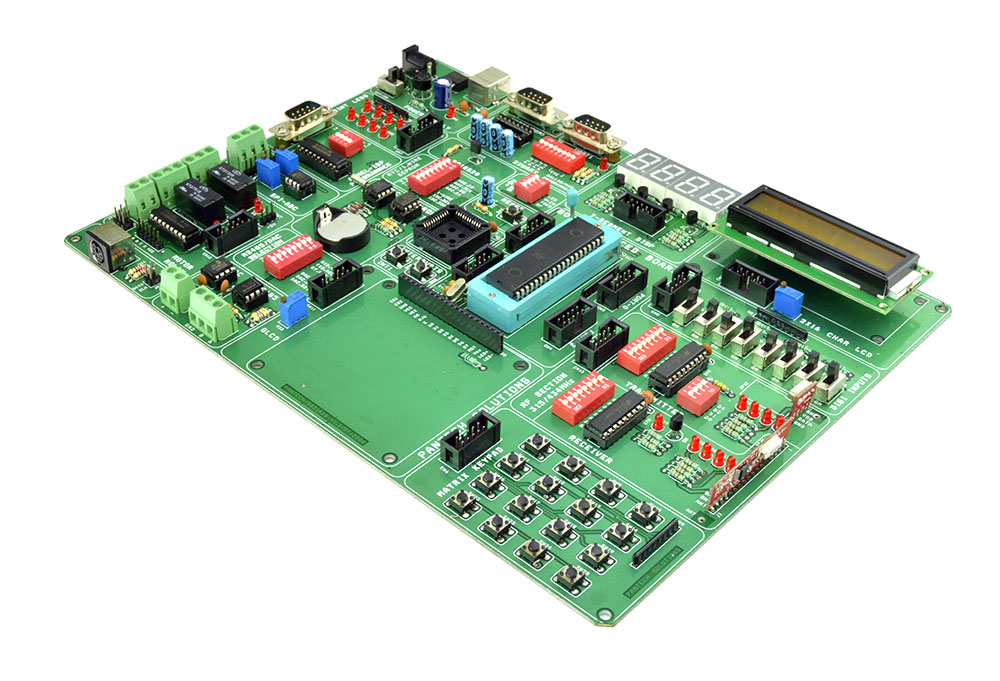

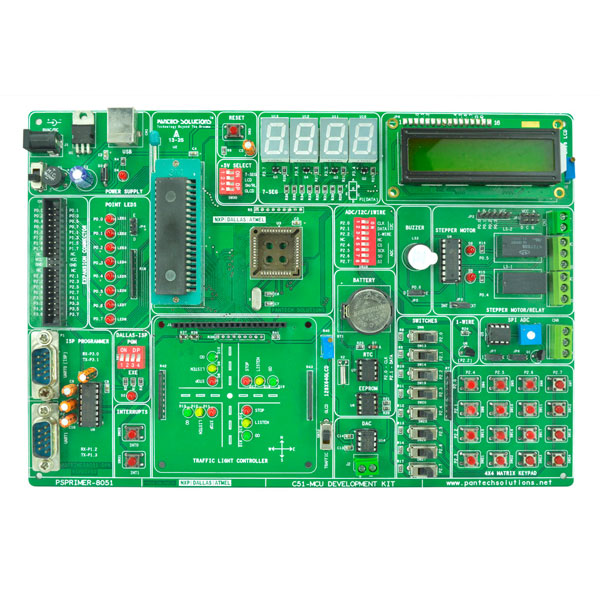

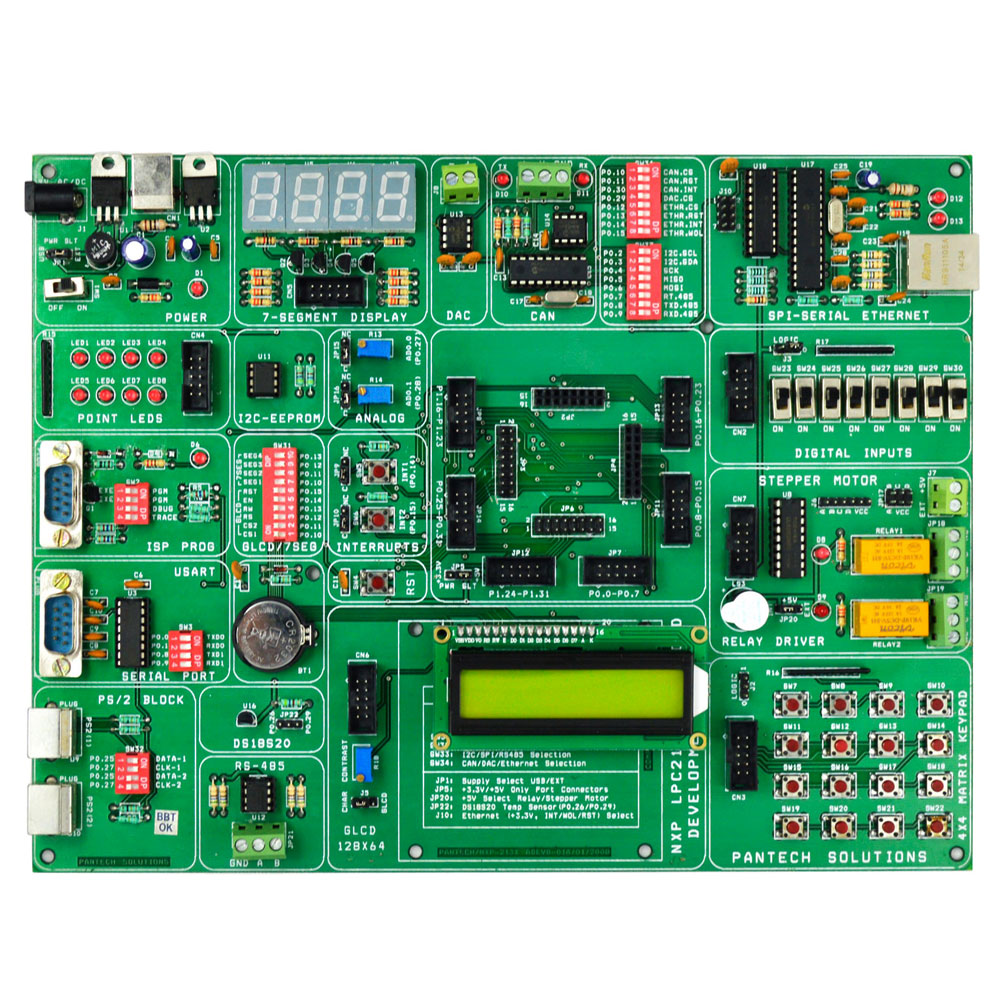

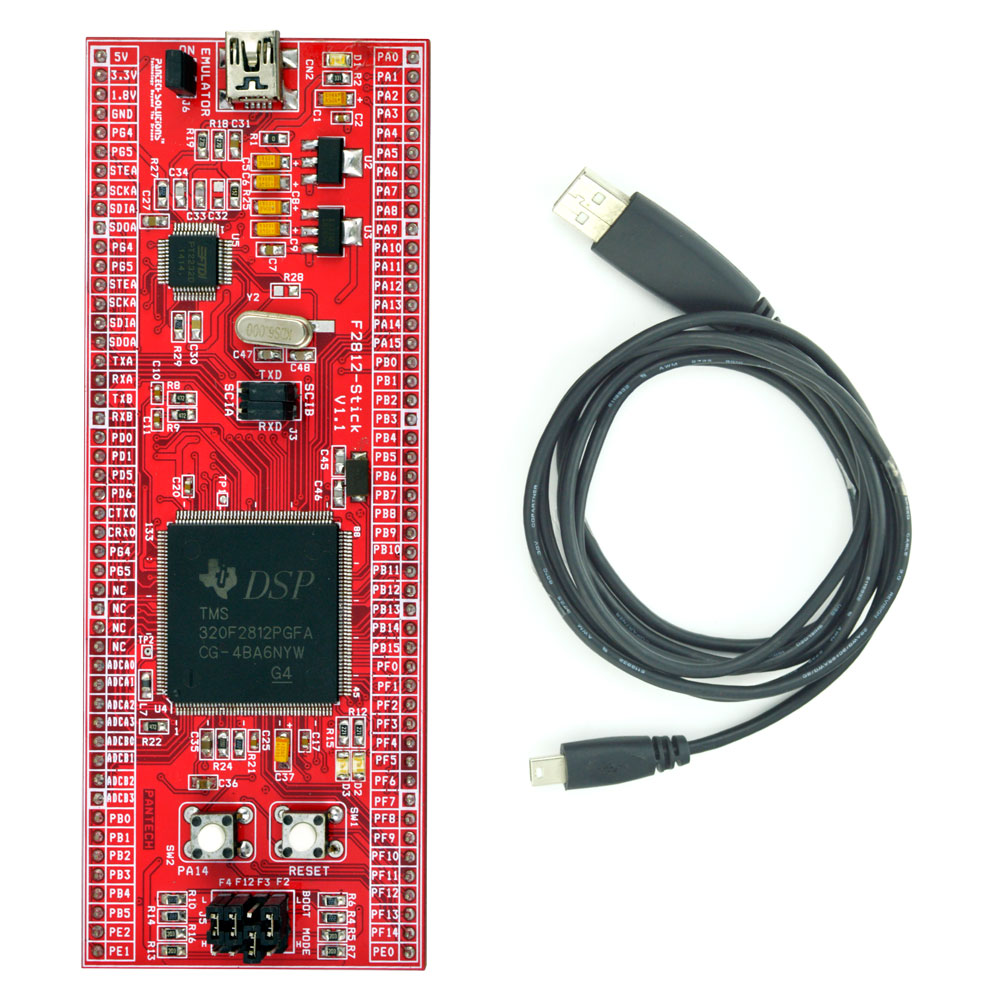

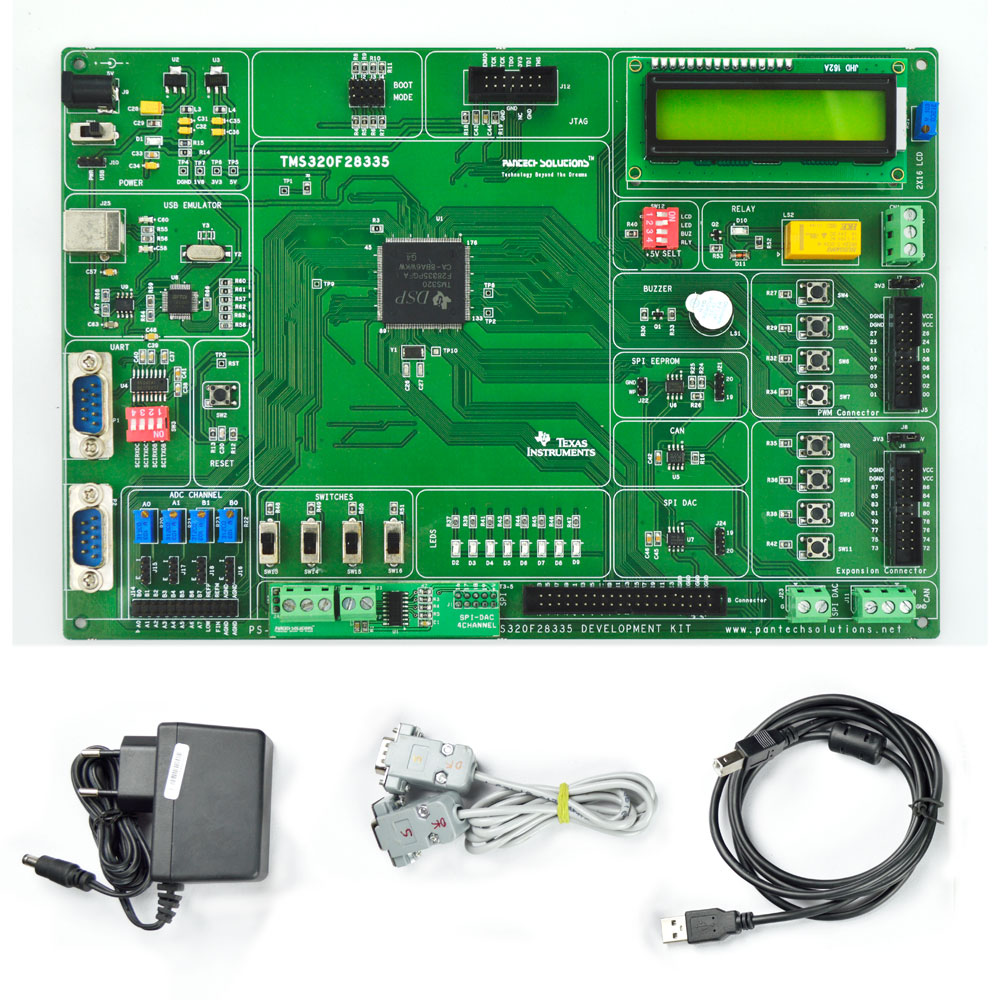

You can also try building similar FSMs in your VLSI Lab using the FSM Trainer Kit from Pantech.

About Author:

A. Manikandan is an RTL Engineer at Pantech India Solutions Pvt. Ltd. With a strong passion for digital design ,FPGAs and ASIC bus protocols. he specializes in FPGA and hardware development, sharing insights to bridge the gap between academia and industry.

You can adjust the second line to reflect any specific expertise or areas of interest you wish to highlight!

Looking Ahead: Collaborate With Us

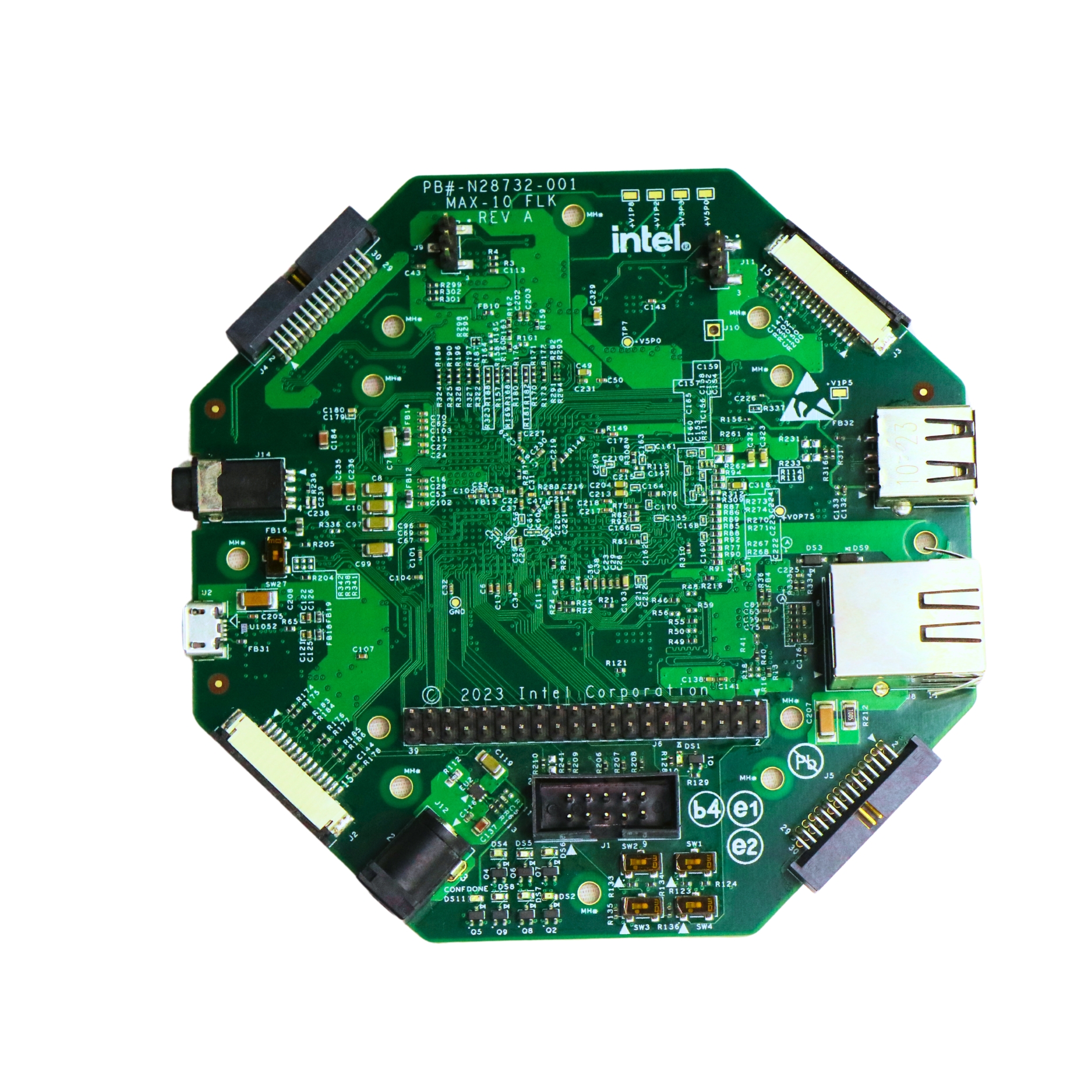

- Try building this Full Adder on the Intel MAX10 FLK FPGA board and visualize the simulation results in real-time.

- Want to build a complete multi-bit adder? Explore our beginner-friendly Verilog series at Pantech eLearning.

- Looking for hands-on training? Join our FPGA/VLSI Internship Program and take your digital design skills tothe next level!

- Email: sales@pantechmail.com

- Website: pantechelearning.com

- Exploring EV models & Battery Management Systems

- Deep dive into autonomous systems & Steer-by-Wire tech

Let’s innovate together—and prepare the next generation of tech leaders.

Digital Electronics

Digital electronics

click here

Boolean Algebra and Logic Gates.

click here...

Implementing and Simulating the OR Gate.

click here

Designing XOR Logic in Verilog

click here

Building the NOR Gate in Verilog

click here

Designing the NAND Gate.

click here

Designing a Half Adder in Verilog

click here

Building a Ripple Carry Adder in Verilog.

click here

Designing a 2x1 Multiplexer in Verilog

click here

Carry look ahead.

click here

Comparator in verilog.

click here

Decoder

click here

Designing a Binary Adder

click here

- All Projects

- Product